- Vertical Slit Field Effect Transistor in ultra-low power applications

- Can pin access limit the footprint scaling?

- A Low Energy Network-on-Chip Fabric for 3-D Multi-Core Architectures

- Investigation of emerging middle-of-line poly gate-to-diffusion contact reliability issues

- Metrics for characterizing machine learning-based hotspot detection methods

- A study on cell-level routing for VeSFET circuits

- On Cell Layout-Performance Relationships in VeSFET-Based, High-Density Regular Circuits

Research

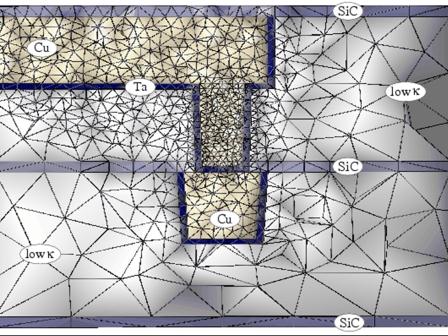

Electromigration (EM) reliability

Principal Investigator: Malgorzata Marek-Sadowska

Students: Di-an Li, Zhong Guan

Sponsors: SRC, IBM, NSF.

Abstract: EM is becoming a serious problem for integrated circuit due to feature size shrinking. Interconnects, especially vias, in Power/Ground (P/G) network suffer from significant EM degradation as they carry large current. In this project, we study EM effect on P/G vias, considering uneven current distribution in via array and time-varying current loads. Our target is to detect hotspot via that is prone to EM failure and IR drop sensitive, and intelligently fix detected hotspot vias.

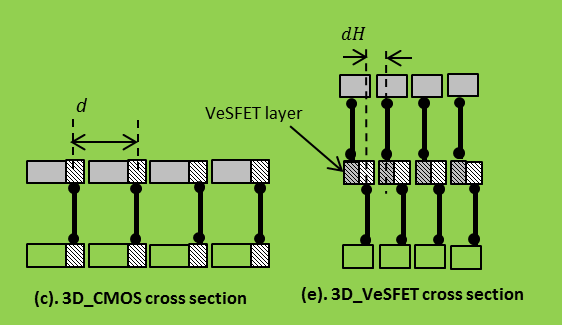

Heterogeneous 3D chip

Principal Investigator: Malgorzata Marek-Sadowska

Students: Vivek S Nandakumar

Sponsors: SRC.

Abstract: Heterogeneous 3D chip with processor cores and cache blocks implemented in CMOS and NoC fabric in VeSFET technology shows significant improvements in all network parameters including latency, power, and energy consumption compared to other practical 3D NoC.

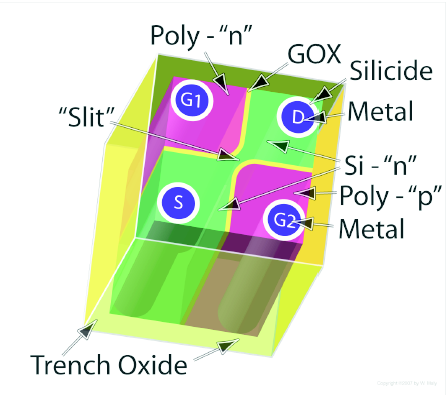

Physical design for VeSFET based circuits

Principal Investigator: Malgorzata Marek-Sadowska

Students: Xiang Qiu

Past Students: Yi-Wei Lin

Collaborator: Prof. Wojciech Maly (CMU)

Abstract: Vertical Slit Field Effect Transistor (VeSFET) is a novel twin-gate 3D device. VeSFETs are very attractive for low power applications because they have very small gate capacitance and extremely low leakage current. Layouts of VeSFET ICs are very different from traditional CMOS. Transistors are packed into regular arrays with much higher density than CMOS ICs, leading to smaller footprint, shorter interconnects, hence higher performance and lower power. Currently, our research topics include VeSFET physical design (placement & routing), testing strategies and low power applications.

Testing of Analog Components in SoCs

Principal Investigator: Malgorzata Marek-Sadowska

Students: Samantha Alt

Sponsors: SRC

Abstract: Analog components in system on chip designs (SoC) have proven to be very difficult to test within the digital design verification flow. These components are simulated and verified using SPICE, which can be very time consuming for more complex components. When targeting the behavior of the system it is critical that the analog components work as intended within the digital system. Unfortunately, current analog modeling techniques require expert knowledge and existing EDA tools cannot behaviorally model analog circuits working in conjunction with the digital components. We propose a machine learning method that will automatically create a behavioral System Verilog macromodel that removes the need for any SPICE simulation and can be tested using available EDA digital design tools.

These links should point to the same links in people.. 1. 2. 3.